H.265 / MPEG-HEVC is the newest video coding standard, which provides a bitrate reduction of up to 50% compared to its ancestor H.264/AVC. This coding gain is achieved by introducing new or enhanced coding tools raising on the other hand the computational requirements for implementations accordingly.

Our research focuses on finding optimal hardware architectures for different H.265 / MPEG-HEVC application fields targeting minimal resource utilization of the underlying technology. To reach the goal of finding architectures providing the highest power efficiency we're strongly committed to pure hardwired implementations and application specific processor cores.

HEVC Main Profile Decoder

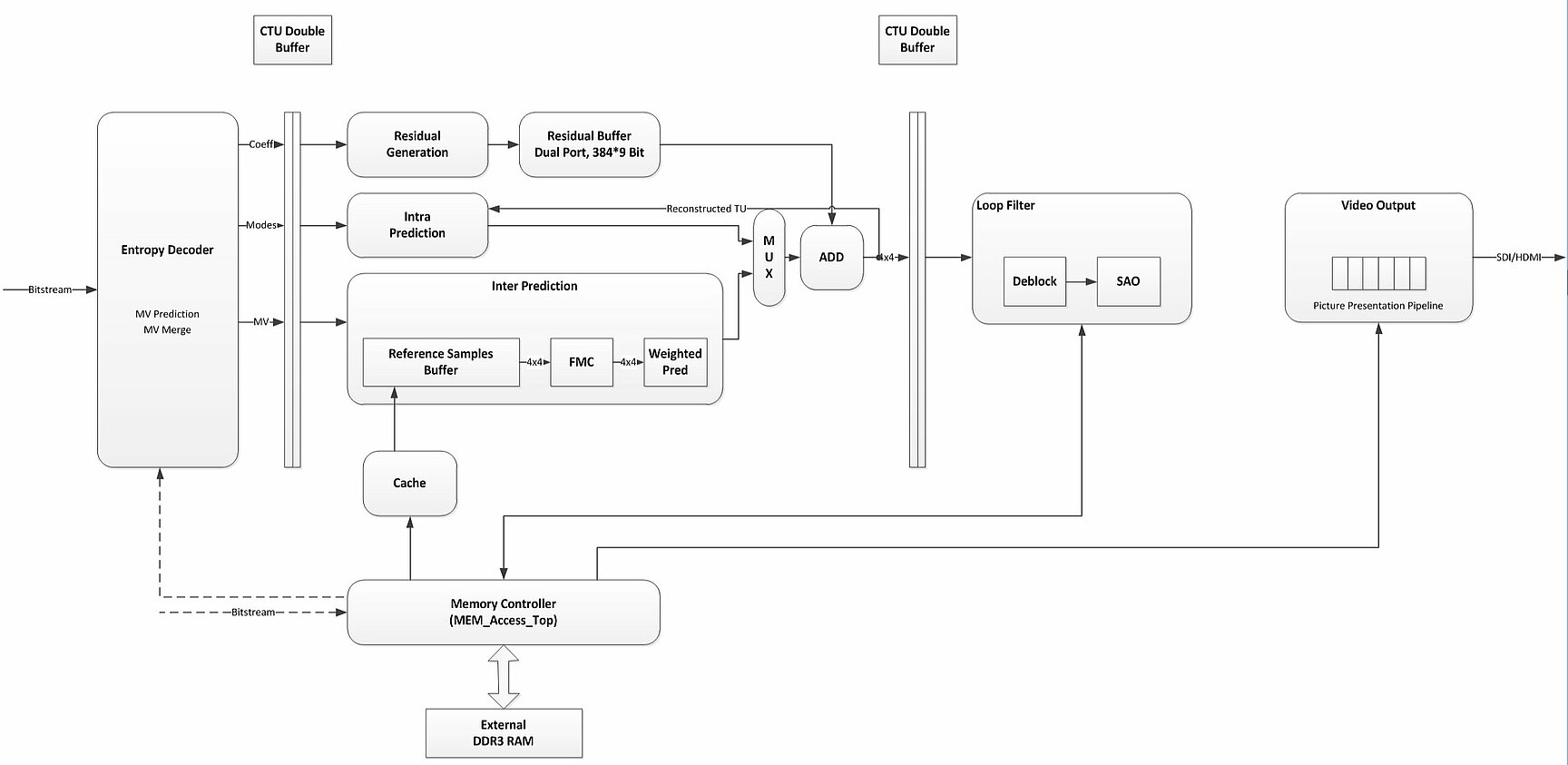

Based on our HEVC Low Latency Decoder we've implemented a highly optimized H.265 / MPEG-HEVC HM11 compliant HEVC Main Profile decoder suited for high end FPGAs, which supports all prediction modes and a full featured CABAC entropy decoder. The decoder is completely hardware based and works without using an additional processor core, which reduces the computational load of an application processor in a SoC architecture.

The design is currently implemented on an Altera StratixV FPGA using a DDR3 external memory. For demonstration purposes we've used an off the shelf evaluation board available form Altera featuring a HDMI output interface card.

In this configuration the decoder achieves realtime performance of up to 1080p60 at an internal clock frequency of approx. 150 Mhz demanding a logic utilization of approx. 66k ALMs.

The decoder will be showcased at IBC 2013 at the FhG-HHI booth.

HEVC Low Latency Intra Only Decoder

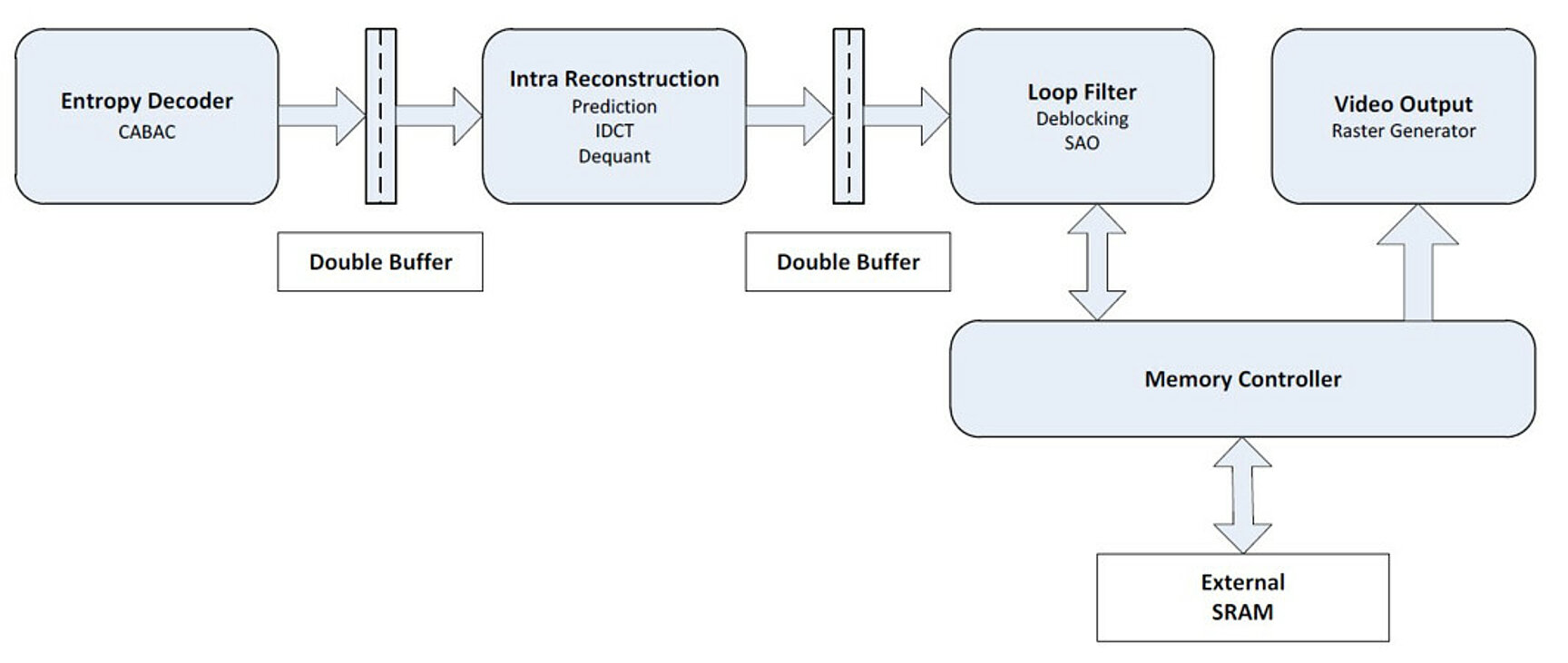

As a first experiment we've implemented a highly optimized H.265 / MPEG-HEVC HM10 compliant ultra low delay decoder IP core, which supports all intra coding modes and a full featured CABAC decoder. The decoder is completely hardware based, which means no additional processor core is incorporated in the decoding process. The design is currently implemented on an Altera Stratix 4 FPGA and features a very low resource utilization by providing real-time performance for full HD resolution (1080p30) at a clock frequency of below 150 MHz and opens the path towards low power implementations. The decoder features SDI and HDMI video output interfaces and an IP based streaming interface for bitstream input.